8086 MICROPROCESSORS

8086

MICROPROCESSORS

8086 Microprocessor is an enhanced version of 8085 Microprocessor

that was designed by Intel in 1976. It is a 16-bit Microprocessor having 20

address lines and16 data lines that provides up to 1MB storage. It consists of

powerful instruction set, which provides operations like multiplication and

division easily.

It supports two modes of operation, i.e. Maximum mode and

Minimum mode. Maximum mode is suitable for system having multiple processors

and Minimum mode is suitable for system having a single processor.

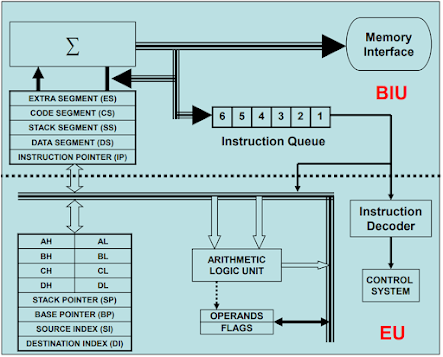

Figure: Architecture of 8086 Microprocessors

8086 Microprocessor is

divided into two functional units, i.e., EU (Execution Unit)

and BIU (Bus Interface Unit).

EU (Execution Unit):

Execution unit gives instructions to BIU stating

from where to fetch the data and then decode and execute those instructions.

Its function is to control operations on data using the instruction decoder

& ALU. EU has no direct connection with system buses as shown in the above figure;

it performs operations over data through BIU.

ALU:

It handles all arithmetic and logical

operations, like +, −, ×, /, OR, AND, NOT operations.

Flag Register:

It is a 16-bit register that behaves like a

flip-flop, i.e. it changes its status according to the result stored in the

accumulator. It has 9 flags and they are divided into 2 groups − Conditional

Flags and Control Flags.

General Purpose Register:

There are 8 general purpose registers, i.e., AH,

AL, BH, BL, CH, CL, DH, and DL. These registers can be used individually to

store 8-bit data and can be used in pairs to store 16bit data. The valid

register pairs are AH and AL, BH and BL, CH and CL, and DH and DL. It is

referred to the AX, BX, CX, and DX respectively.

Stack Pointer Register:

It is a 16-bit register, which holds the address

from the start of the segment to the memory location, where a word was most

recently stored on the stack.

BIU (Bus Interface Unit):

BIU takes care of all data and addresses

transfers on the buses for the EU like sending addresses, fetching instructions

from the memory, reading data from the ports and the memory as well as writing

data to the ports and the memory. EU has no direction connection with System

Buses so this is possible with the BIU. EU and BIU are connected with the

Internal Bus.

It has the following functional parts −

·

Instruction queue − BIU contains the instruction queue. BIU

gets upto 6 bytes of next instructions and stores them in the instruction

queue. When EU executes instructions and is ready for its next instruction,

then it simply reads the instruction from this instruction queue resulting in

increased execution speed.

·

Fetching the next instruction while the current instruction

executes is called pipelining.

·

Segment register − BIU has 4 segment buses, i.e. CS, DS,

SS& ES. It holds the addresses of instructions and data in memory, which

are used by the processor to access memory locations. It also contains 1

pointer register IP, which holds the address of the next instruction to execute

by the EU.

·

Instruction pointer − It is a 16-bit register used to hold the

address of the next instruction to be executed.

Comments

Post a Comment